# **Single-Core Processor**

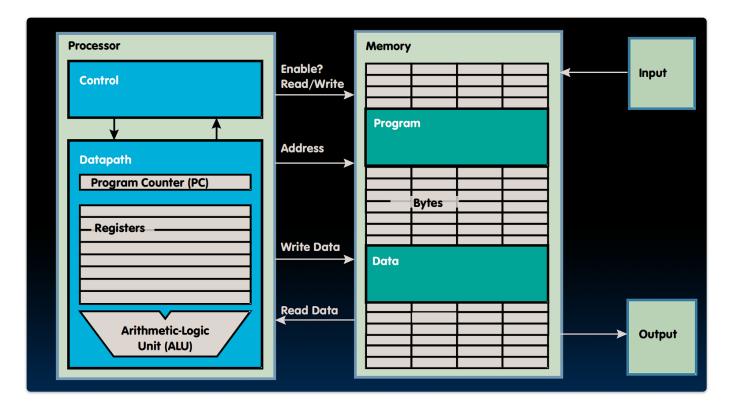

# CPU

The active part of the computer that does all the work.

- Data manipulation.

- Decision making.

## Datapath

Portion of the processor that contains hardware necessary to perform operations required by the processor(the body)

## Control

Portion of the processor that tells the datapath what needs to be done.(the brain)

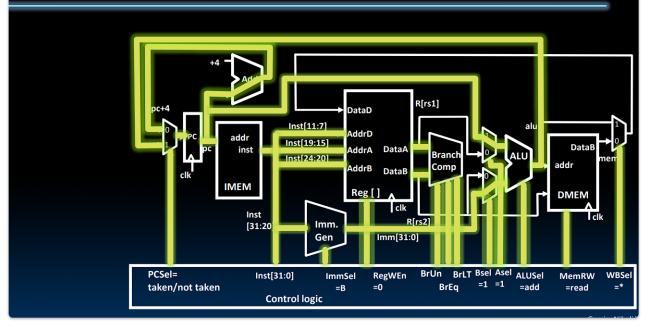

# One-Instruction-Per-Cycle RISC-V Machine

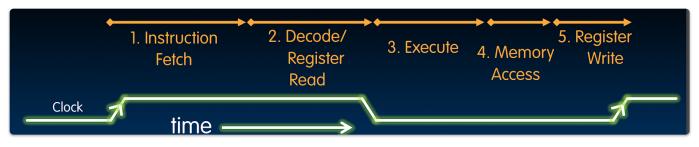

# **Stage of the Datapath**

break up the process of "executing an instruction" into stages, and then connect the stages to create the whole datapath.

- Stage 1: Instruction Fetch (IF)

- Stage 2: Instruction Decode (ID)

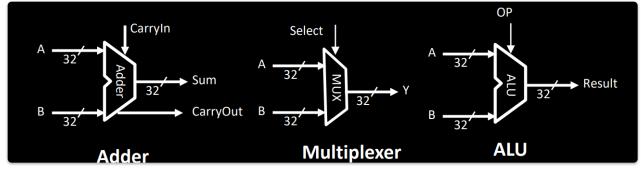

- Stage 3: Execute (EX) ALU (Arithmetic-Logic Unit)

- Stage 4: Memory Access (MEM)

- Stage 5: Write Back to Register (WB)

These five stages are executed in one clock cycle, which is called One-instruction-Per-cycle.

Register write will be executed at the next rising edge of clock.

## **Datapath components**

### COMBINATIONAL

Combinational elements

### STATE AND SEQUENCING

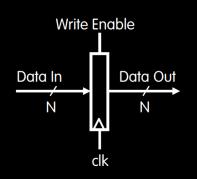

Register

- Register

- Write Enable:

- Low (or deasserted) (0):

Data Out will not change

- Asserted (1): Data Out will become Data In on positive edge of clock

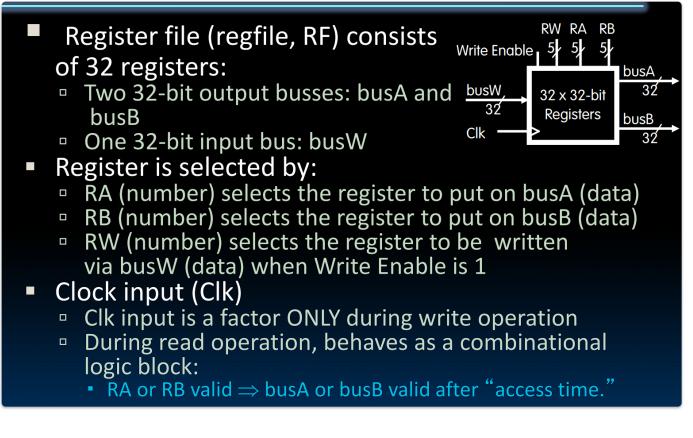

#### **Register File**

### Consists of 32 registers

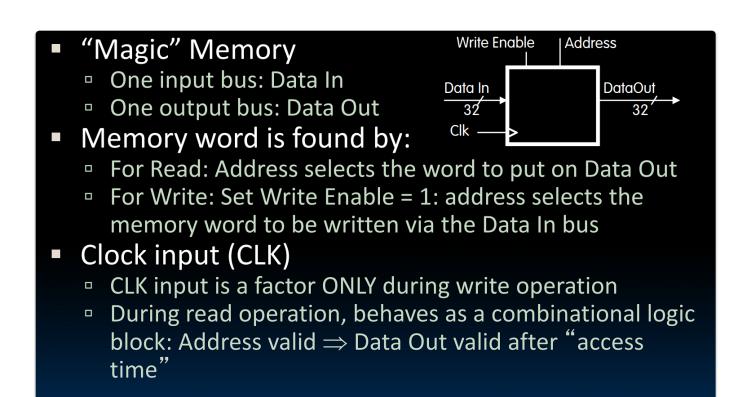

Memory

For **read** operation we **don't** need to wait for the clock, just put the address of register or memory, the data will automatically pop up.

For **write** operation we need to wait for the rising edge of the clock to write data.

Each instruction during execution reads and updates the state of

- 1. registers

- 2. pc

- 3. Memory

# Datapath

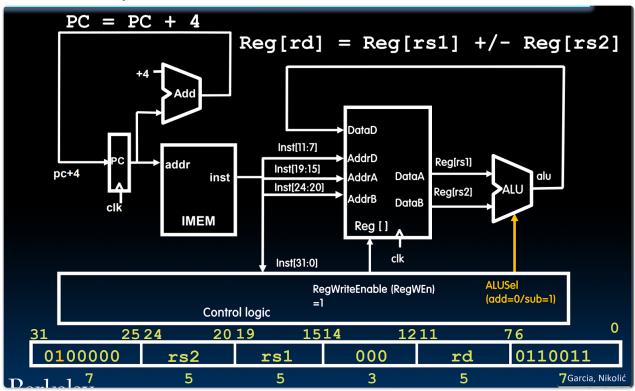

**R-Format Datapath**

### **Review**

| 31 30 29 28 27 26 25                                                                                            | 24 23 22 21 20 | 19 18 17 16 15 | 14 13 12   | 10 9 8 7   | 6 5 4 3 2 1 0 |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|----------------|----------------|------------|------------|---------------|--|--|--|

| R-format : ALU                                                                                                  |                |                |            |            |               |  |  |  |

| [31:25]                                                                                                         | [24:20]        | [19:15]        | [14:12]    | [11:7]     | [6:0]         |  |  |  |

| 7                                                                                                               | 5              | 5              | 3          | 5          | 7             |  |  |  |

| func7                                                                                                           | rs2            | rs1            | func3      | rd         | opcode        |  |  |  |

| 000000                                                                                                          | rs2            | rs1            | 000 : ADD  | rd         | 0110011:OP-R  |  |  |  |

| 0100000                                                                                                         | rs2            | rs1            | 000 : SUB  | rd         | 0110011:OP-R  |  |  |  |

| 000000                                                                                                          | rs2            | rs1            | 001 : SLL  | rd         | 0110011:OP-R  |  |  |  |

| 000000                                                                                                          | rs2            | rs1            | 010 : SLT  | rd         | 0110011:OP-R  |  |  |  |

| 000000                                                                                                          | rs2            | rs1            | 011 : SLTU | rd         | 0110011:OP-R  |  |  |  |

| 000000                                                                                                          | rs2            | rs1            | 100 : XOR  | rd         | 0110011:OP-R  |  |  |  |

| 000000                                                                                                          | rs2            | rs1            | 101 : SRL  | rd         | 0110011:OP-R  |  |  |  |

| 0100000                                                                                                         | rs2            | rs1            | 101 : SRA  | rd         | 0110011:OP-R  |  |  |  |

| 000000                                                                                                          | rs2            |                | 110 : OR   | rd         | 0110011:OP-R  |  |  |  |

| 000000                                                                                                          | rs2            | rs1            | 111 : AND  | rd         | 0110011:OP-R  |  |  |  |

| <ul> <li>E.g. Addition/subtraction add rd, rs1, rs2<br/>R[rd] = R[rs1] + R[rs2]<br/>sub rd, rs1, rs2</li> </ul> |                |                |            |            |               |  |  |  |

|                                                                                                                 |                |                | R[rd]      | = R[rs1] - | - R[rs2]      |  |  |  |

Garcia, Nikol

0

| Berkeley<br>UNIVERSITY OF CALIFORNIA | RISC-V (20) |

|--------------------------------------|-------------|

|                                      |             |

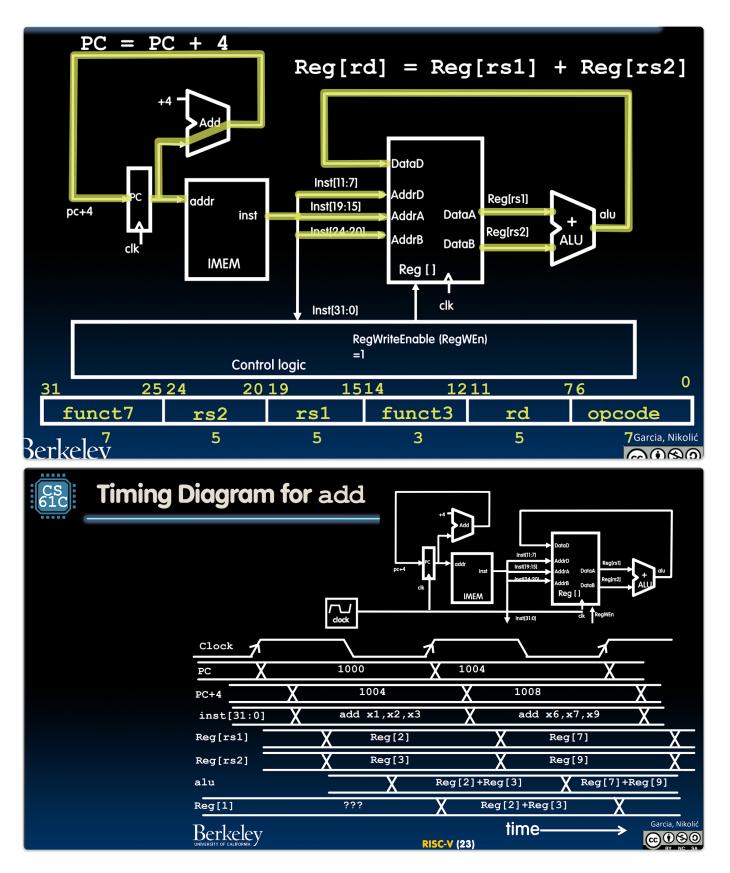

## Implementing the add instruction

| 31 25            | 524 20 | )19 15 | 14 12  | 211 | 76      | 0  |  |

|------------------|--------|--------|--------|-----|---------|----|--|

| funct7           | rs2    | rs1    | funct3 | rd  | opcode  |    |  |

| 7                | 5      | 5      | 3      | 5   | 7       |    |  |

| <u>31 25</u>     | 24 20  | 19 15  | 14 12  | 11  | 76      | 0  |  |

| 0000000          | rs2    | rs1    | 000    | rd  | 0110011 |    |  |

| 7                | 5      | 5      | 3      | 5   | 7       |    |  |

| add              | rs2    | rs1    | add    | rd  | Reg-Reg | OP |  |

|                  |        |        |        |     |         |    |  |

| add rd, rs1, rs2 |        |        |        |     |         |    |  |

Instruction does two changes

1. Reg[rd] = Reg[rs1] + Reg[rs2]

#### 2. **PC +=4**

#### DATAPATH FOR ADD

#### DATAPATH FOR SUB/ADD

sub almost the same as add, except now we need to subtract operands.

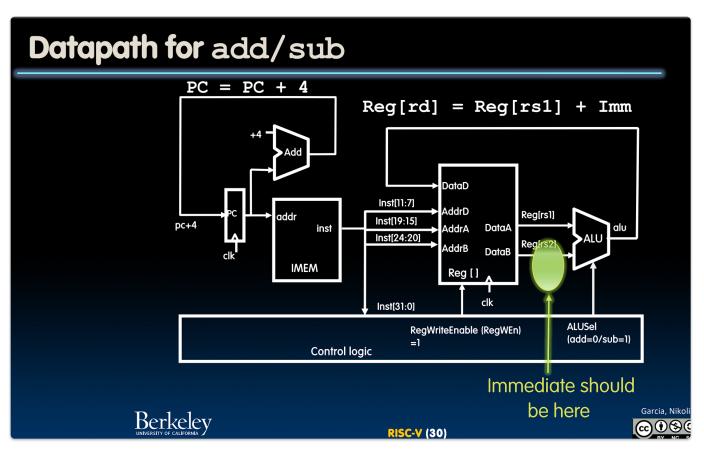

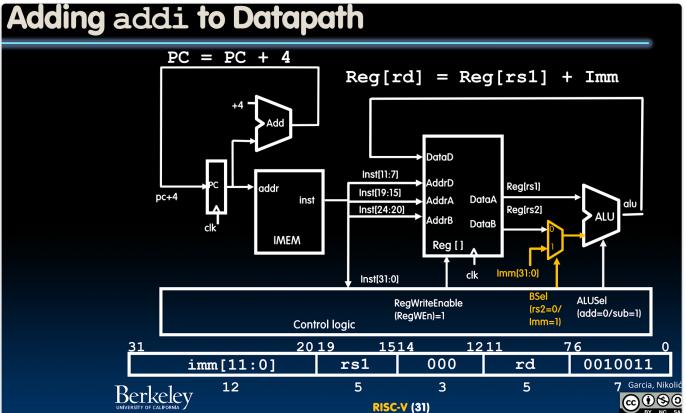

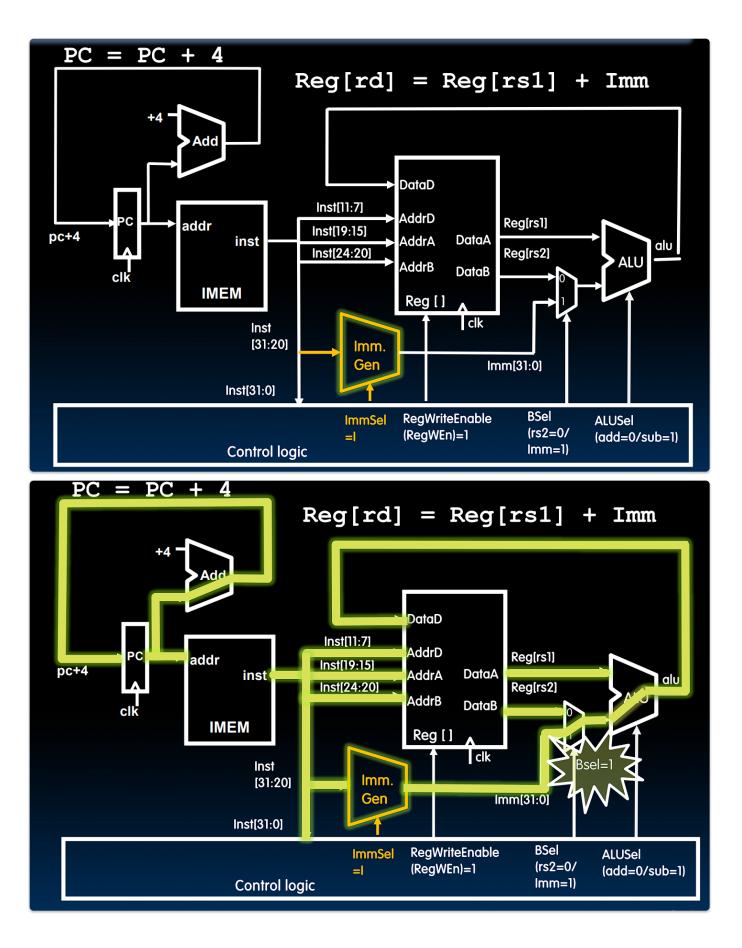

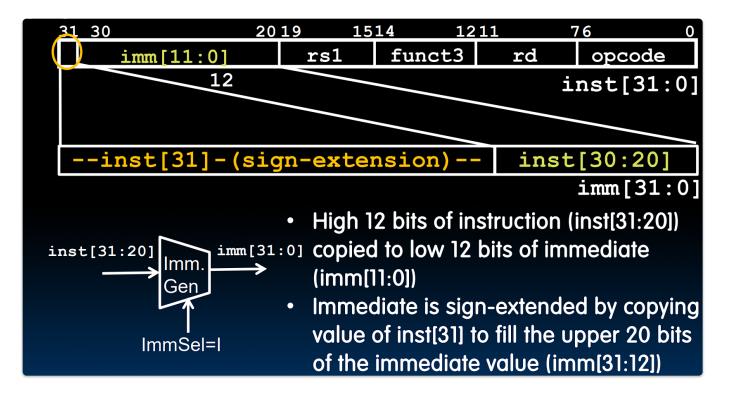

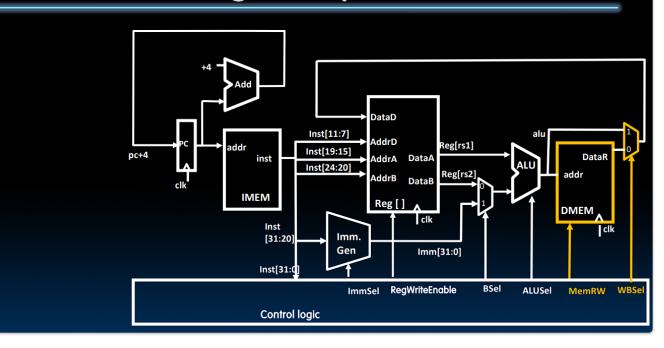

## **I-Format Datapath**

Addi

# Add a Mux at there

load

|           | RISC-V Assembly In | lw x14    | , 8(x2)    |           |           |

|-----------|--------------------|-----------|------------|-----------|-----------|

| <u>31</u> | 20                 | 19 15     | 14 12      | 11 7      | 6 0       |

|           | imm[11:0]          | rs1       | funct3     | rd        | opcode    |

|           | 12<br>offset[11:0] | 5<br>base | 3<br>width | 5<br>dest | 7<br>LOAD |

|           | 00000001000        | 00010     | 010        | 01110     | 0000011   |

|           | imm=+8             | rs1=2     | lw         | rd=14     | LOAD      |

- The 12-bit signed immediate is added to the base address in register rs1 to form the memory address

- This is very similar to the add-immediate operation but used to create address not to create final result

### R+I Arithmetic/Logic Datapath

- to 52 bits before writing back to reg

- It is just a mux + a few gates

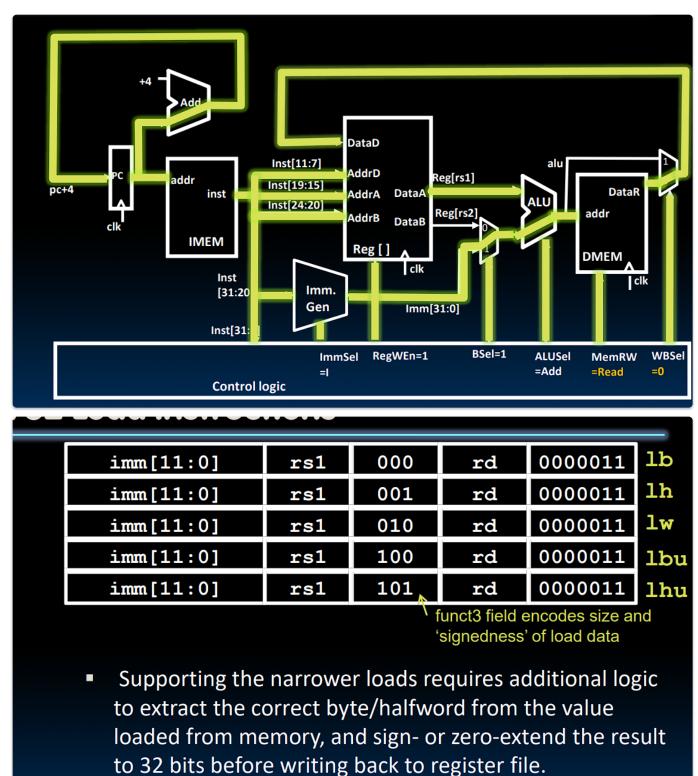

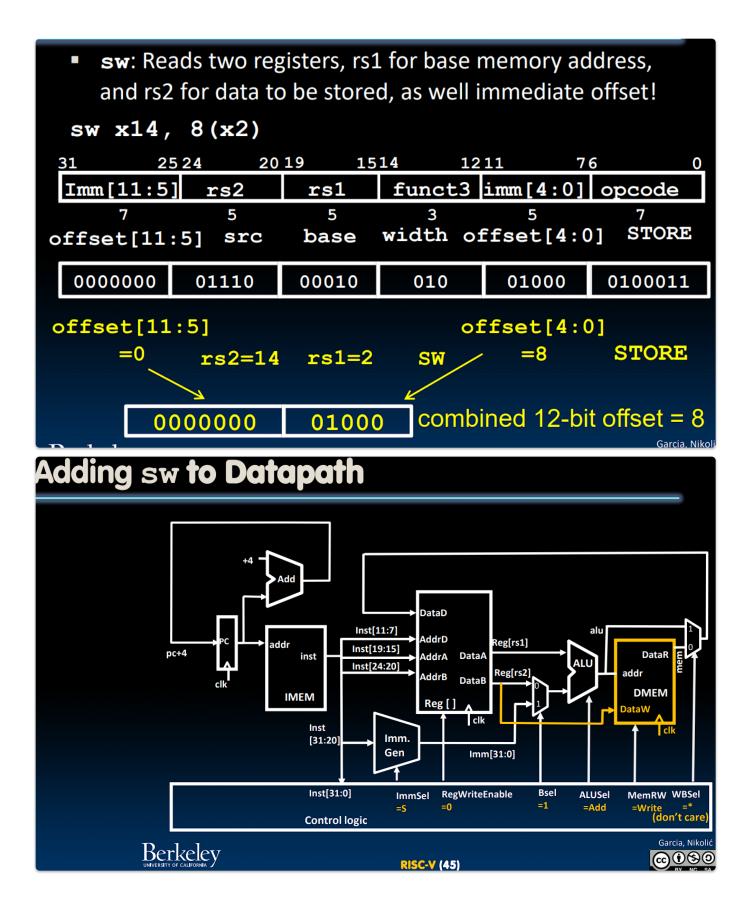

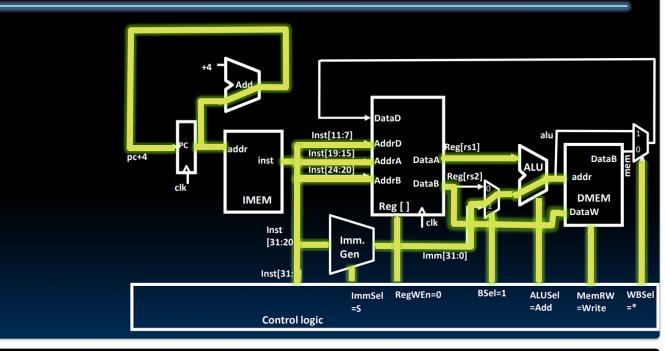

# **S-Format**

#### ADDING SW INSTRUCTION

## Adding sw to Datapath

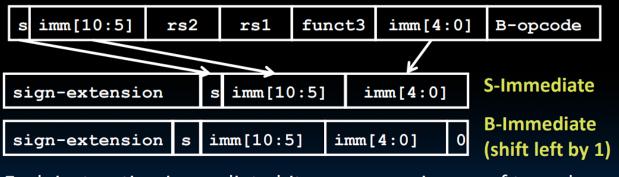

## I+S Immediate Generation

| 3 <u>1 30 25 2</u>  | 24 20    | 19 15    | 14 12    | 11 7                                    | 6 0        |

|---------------------|----------|----------|----------|-----------------------------------------|------------|

| imm[1]              | 1:0]     | rs1      | funct3   | rd                                      | I-opcode   |

| imm[11:5]           | rs2      | rs1      | funct3   | imm[4:0]                                | S-opcode   |

|                     |          |          |          |                                         | inst[31:0] |

|                     |          |          | 5        | 5×                                      |            |

| 1 🔨                 | 6        |          |          |                                         |            |

|                     |          |          |          | /s ———————————————————————————————————— |            |

| <u> </u>            |          |          | <u>×</u> |                                         |            |

| inst[31]            | (sign ex | tension) | inst[30  | :25] i                                  | nst[24:20] |

| <pre>inst[31]</pre> | (sign ex | tension) | inst[30  | :25] i                                  | nst[11:7]  |

| 31                  |          | 1:       | 10       | 54                                      | 0          |

|                     |          |          |          |                                         | imm[31:0]  |

- Just need a 5-bit mux to select between two positions where low five bits of immediate can reside in instruction

- Other bits in immediate are wired to fixed positions in instruction

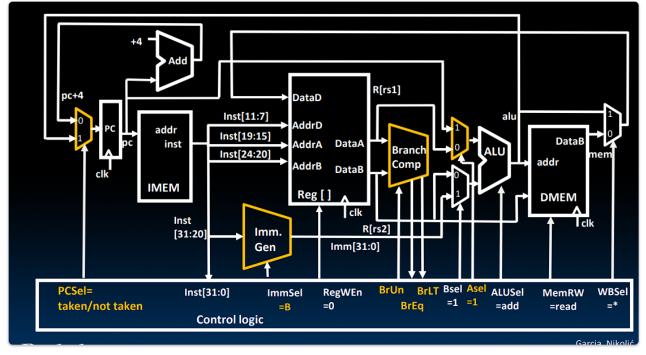

## **B-Format**

| 31      | 30                                                                                                                                                     | 25 2 | 4 20 | 1915 | 514 | 12 1 | 1     | 8     | 7        | 6         | 0   |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-----|------|-------|-------|----------|-----------|-----|

| imm[12] | imm[1                                                                                                                                                  |      |      |      |     |      |       | 1] in | am [ 1 1 | ] opc     | ode |

| 1       |                                                                                                                                                        | 6    | 5    | 5    | 3   |      | 4     |       | 1        | 7         |     |

| offs    | et[12]:                                                                                                                                                |      | rs2  |      | fur | nct3 | offse | t[4:  | 1 11     | BRAN<br>] | ICH |

| -       | <ul> <li>B-format is mostly same as S-Format, with two<br/>register sources (rs1/rs2) and a 12-bit<br/>immediate imm[12:1]</li> </ul>                  |      |      |      |     |      |       |       |          |           |     |

| •       | <ul> <li>But now immediate represents values</li> <li>-4096 to +4094 in 2-byte increments</li> </ul>                                                   |      |      |      |     |      |       |       |          |           |     |

|         | <ul> <li>The 12 immediate bits encode even 13-bit signed<br/>byte offsets (lowest bit of offset is always zero, so<br/>no need to store it)</li> </ul> |      |      |      |     |      |       |       |          |           |     |

Need to compute PC+IMMEDICATE and to compare values of rs1 and rs2

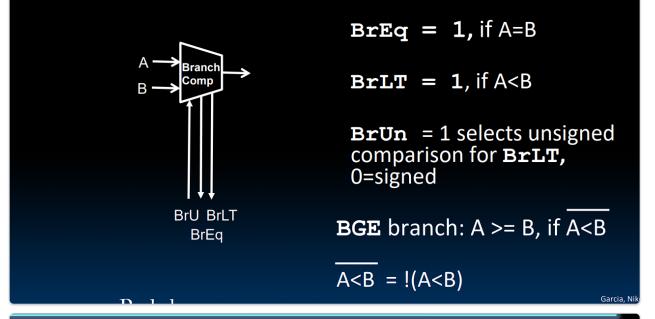

#### **Branch Comparator**

12-bit immediate encodes PC-relative offset of -4096 to +4094 bytes in multiples of 2 bytes

Standard approach: Treat immediate as in range -2048..+2047, then shift left by 1 bit to multiply by 2 for branches

Each instruction immediate bit can appear in one of two places in output immediate value – so need one 2-way mux per bit

# Lighting Up Branch Path